# Design Of DSBSC Modulator Using MOS Transistor And Analysis Of Its Power, Delay, Frequency Response And Thermal Noise Due To Channel Resistance Of MOS

Bipasha Chakrabarti<sup>1</sup>, Tarun Samadder<sup>2</sup>, Debanjana Ray, Sampa Das Electronics and Communication Engineering Department Gargi Memorial Institute of Technology Kolkata, India

bcbipasha@gmail.com<sup>1</sup> samaddertarun@gmail.com<sup>2</sup>,debanjanaray11@gmail.com,csampa\_garia@rediffmail.com

**Abstract**— This paper presents the design of double side band suppressed carrier (DSBSC) modulator using MOS transistors at deep sub micron level. Modulator part of the circuit has been designed using two transistor only. Working principle of the circuit has been presented qualitatively. Graphical representation of instantaneous power drawn from message signal source has been focused . Power consumption across the resistances in the inverting amplifier section has been measured. It is also measured the delay from carrier input instance to modulated output instance . Frequency response of the circuit has been plotted . Finally it is analysed the thermal noise of the circuit at output due to channel resistance of MOS transistor .All the measurements and analysis are performed using Tanner SPICE (T-SPICE) software . It is found that power drawn from the message signal source is of the order of 10<sup>5</sup> Watt . Said delay is of the order of pico second . The circuit exhibits very wide frequency range of operation without attenuation and higher cut off frequency is around 188GHz. From noise analysis it is found that thermal noise at output due to channel resistance is of the order of 10<sup>-24</sup> Volt<sup>2</sup> /Hz.

Index Terms — DSBSC, modulation, delay, power, thermal noise, frequency response, T-SPICE, Schematic

# **1. INTRODUCTION**

Modulation is a process by which some

characteristics of a signal known as carrier signal is varied according to the base band signal or modulating signal or message signal . In this paper DSBSC modulator is designed using MOS transistor with feature size of 150nm. The circuit is designed to operate with square wave as carrier input. Carrier source is basically a clock pulse generator . CMOS inverter is designed to invert clock pulse to be used in the circuit . One buffer amplifier is designed with one voltage controlled voltage source having 2 M $\Omega$  input resistance and 75  $\Omega$  output resistance and open loop gain of 2×10<sup>5</sup>. With same input and output resistance another voltage controlled voltage source is used to realize inverting amplifier having overall gain equals to -1 .Inverting amplifier is used only to change the phase of the modulating signal by 180°. Buffer amplifier is used to avoid loading effect . Power, delay, thermal noise for specific part of

the circuit are analyzed. Frequency of response of the circuit is also plotted.

## II. SCHEMATIC DIAGRAM AND OPERATION OF THE CIRCUIT

#### A. Circuit description

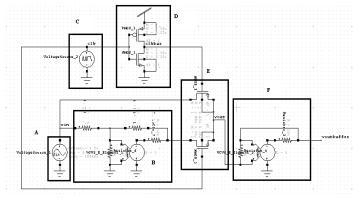

The schematic diagram of proposed DSBSC modulator circuit is shown in figure1.

Figure 1. Schematic diagram of DSBSC Modulator

The whole circuit shown in figure 1 is divided into five blocks . Block A ,B,C,D ,E and F. Block A is consisting of message signal source. Block B is an inverting amplifier realised using voltage controlled voltage source having 2 M $\Omega$  input resistance , 75  $\Omega$  output resistance , open loop gain of 2×10<sup>5</sup> and two external resistances each of value  $10K \Omega$ . One  $10K \Omega$  resistance is connected between output of amplifier and inverting\_terminal of the amplifier . Another 10 K $\Omega$  resistance is connected between inverting terminal of the amplifier and signal source. So closed loop gain of the inverting amplifier is approximately equals to -1. Block C is for carrier signal source basically a clock pulse generator. Block D is a CMOS inverter used to invert clock pulse .Block E is the heart of the circuit .Here actual DSBSC modulation is performed using two MOS transistor only. Block F is configured for buffer amplifier with a vgoltage controlled voltage source having 2 M $\Omega$ input resistance, 75  $\Omega$  output resistance, open loop gain of shorting externally the output of 2×10⁵ and voltage controlled voltage source to the inverting terminal of the same voltage controlled voltage source . Non inverting terminal of buffer is used to apply signal. So gain of the buffer is approximately equal to 1. Source terminal of Bottom MOS transistor say MNMOS\_2 of block E is connected to message source in block A through block B consisting of an inverting amplifier. Message signal source in the block A is connected to source terminal of the top MOS transistor say transistor MNMOS\_3 in block E of figure 1.From block C carrier signal is connected to gate terminal of bottom MOS transistor of block E of figure 1.Gate terminal of top MOS transistor in the block E is connected to carrier source through a CMOS inverter. Drain terminal of two MOS transistor in the block E is tied together to get DSBSC modulated output .Body terminal of both of transistors in block E are connected to their drain terminal to avoid body bias effect . Output from block E is

connected to the non inverting terminal of buffer amplifier in the block F . Here buffer amplifier is employed to avoid loading effect . Final output is taken from buffer amplifier.

#### B. Circuit operation

To simulate the circuit 1Khz sine is taken as message signal. Clock pulse of frequency 50KHz is taken as carrier signal . When clock is high gate terminal of bottom MOS transistor MNMOS\_2 in the block E is high .So MNMOS\_2 is on and inverted message signal will be passed through MNMOS\_2 to the output of block E. During high time of clock pulse as the CMOS inverter output is low. So gate terminal of top MOS transistor MNMOS\_3 in the block E is low and transistor is off . On the other hand during low time of clock pulse MNMOS\_3 is on and message signal is passed to the output of block E through MNMOS\_3.For repetition of clock pulses and observation for a message signal time period output from block E is a DSBSC modulated wave .Final output is taken from the buffer amplifier .

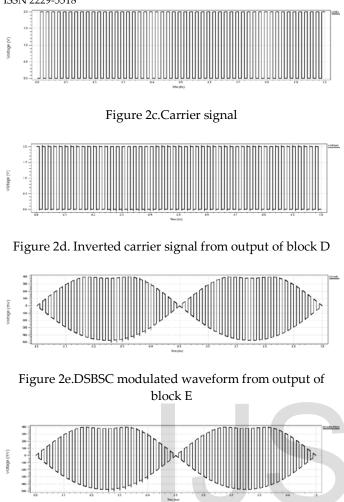

#### C. T-SPICE generated waveform

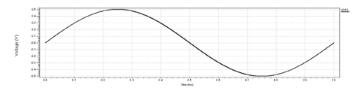

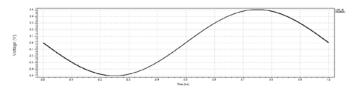

Output waveforms generated by T-SPICE software from different blocks of figure1 are displayed here . Figure 2a & 2b represents message signal and inverted message signal from block A and B block respectively. Carrier signal and inverted carrier signal are represented in figure 2c & 2d respectively .DSBSC modulated output from block E is shown in figure 2e .Output from buffer circuit is shown in figure 2f .

Figure 2a . Message signal

Figure 2b.Inverted message signal from out put of block B

Figure 2f. DSBSC modulated waveform from buffer output termina

#### **III. ANALYSIS OF POWER**

In this article power drawn from message source, power consumption in CMOS inverter and power dissipated in two  $10K\Omega$  external resistances in block B have been discussed.

#### A. Power drawn form message source

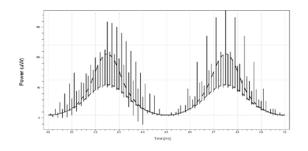

Ideally for any kind of circuit design no power will be drawn from signal source .But practically for all types of circuit design few power is drawn from signal source. In our case nature of instantaneous power drawn from message source is shown in figure 3a .As shown in figure 3a comparatively more power is drawn during off period of clock pulse than high period of clock. During off time of clock MNMOS\_3 transistor in E block is on .As message source is directly connected to source terminal of MNMOS\_3 transistor , comparatively high current is drawn from message source as drawn during on time of clock. When MNMOS\_2 transistor is on during high time of clock comparatively less current is drawn from message source as inverting amplifier input resistance is high compared to the on resistance of MNMOS\_3. In instantaneous power curve of figure 3a some power glitches are also observed during transition of clock pulse .As measured average power drawn from the message source is 2.36×10<sup>-5</sup> Watt.

Figure 3a. Instantaneous power drawn from message source

#### B. Power consumption in CMOS inverter

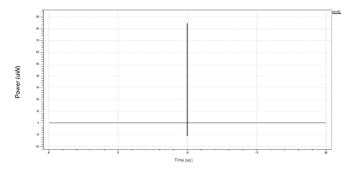

Instantaneous power consumption in CMOS inverter is shown in figure 3b.During transition of clock both NMOS and PMOS transistor of CMOS inverter are on ,VDD is directly connected to ground and maximum power is consumed This is shown in figure 3b like a spike wave .During steady state of clock almost zero power is consumed in CMOS inverter .Average power consumed in CMOS inverter as measured is 2.02×10<sup>-9</sup> Watts.

B. Power dissipated in two 10K  $\Omega$  external resistances in block B

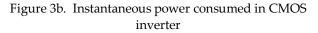

As the value of two resistances are same and almost same current flows through the two resistances power dissipation across the two 10 K $\Omega$  resistances are also same . The nature of instantaneous power dissipated across one of the resistance is shown in figure 3c. Measured Power consumption across the one of the resistance is 1.25  $\times 10^{-5}$  Watt.

Figure 3c. Instantaneous power dissipation across  $10 \mathrm{K}\Omega$  resistance

## IV. DELAY AND FREQUENCY RESPONSE

For any circuit either discrete or integrated circuit in addition with power analysis delay and frequency response analysis is also urgent to measure the performance of the circuit.

#### A. Delay

In our designed DSBSC modulator circuit delay between clock input ( input terminal of CMOS inverter) and output terminal of buffer amplifier has been measured . Amount of delay found is 1.33×10<sup>-12</sup> Sec or 1.33ps.

#### B. Frequency Response

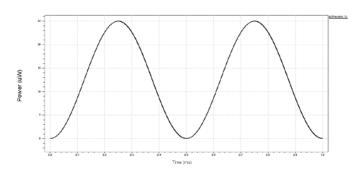

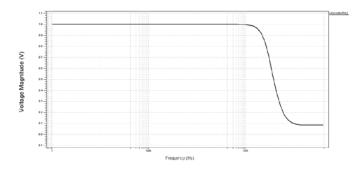

Frequency response is plotted using T-SPICE as shown in figure 3d. It is seen that circuit exhibits very wide frequency response without attenuation . From frequency curve -3dB cut off frequency is approximately 188 GHz.

Figure 3d.Frequency response of DSBSC modulator

# V. THERMAL NOISE DUE TO CHANNEL RESISTANCE OF MOS

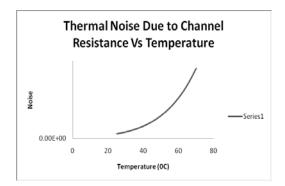

In a circuit noise is unwanted signal .There are several types of noise exists in both integrated circuits and discrete circuits. Among all noises thermal noise and flicker are predominant in integrated circuit. In DSBSC modulator circuit of figure1 only contribution of thermal noise at buffer output due to channel resistance of MNMOS\_2 is measured . It is measured the variation of said thermal noise due to temperature as shown in table 1. Figure 4 is the graphical representation of table1.

|                  | Thermal      |

|------------------|--------------|

| Temperature (0C) | Noise(Square |

|                  | Volt/Hz)     |

| 25               | 1.15E-24     |

| 30               | 1.62E-24     |

| 35               | 2.27E-24     |

| 40               | 3.14E-24     |

| 45               | 4.31E-24     |

| 50               | 5.84E-24     |

| 55               | 7.85E-24     |

| 60               | 1.05E-23     |

| 65               | 1.38E-23     |

| 70               | 1.81E-23     |

Figure 4. Variation of thermal noise at buffer output due to channel resistance of MOS transistor MNMOS\_2

# VI. NETLIST

Overall net list of the circuit of figure1 is presented below.

RResistor 1 N 8 N 4 R=10k RResistor 2 vin N 8 R=10k RResistor 3 N 5 voutbuffer R=75 RResistor 4 voutbuffer vout R=2MEG RResistor\_6 N\_8 Gnd R=2MEG N 9 RResistor\_7 N 4 R=75 MNMOS\_1 clkbar clk Gnd Gnd nh W=0.4 5u L=.15u AD=.3375p AS=.3375p PS=2.4u PD=2.4u MNMOS\_2 N\_4 clk vout vout nh W=0.45u L=.15u AS=.3375p PS=2.4u AD=.3375p PD=2.4u MNMOS\_3 vin clkbar vout vout nh W=0.45u L=.15u AS=.3375p PS=2.4u AD=.3375p PD=2.4u MPMOS 1 clkbar clk Vdd Vdd ph W=.9u L=.15u AS=.675p PS=3.3u AD=.675p PD=3.3u BIT({0101} pw=10u on=2 VVoltageSource\_2 clk Gnd off=0 rt=.01n ft=.01n delay=0 ht=10u lt=10u ) SIN(0 500m 1K 0 0 0) \*VVoltageSource\_1 vin Gnd N 9 Gnd N 8 2E+5 EVCVS E Element 1 Gnd EVCVS E Element 2 Gnd N\_5 vout voutbuffer 2E+5 v12 vin gnd AC 1Vvdd vdd gnd 2 .include "E:\\dual.md" .temp 70 \*.tran .1n 20u \*.power VVoltageSource\_1 .1n 40u dec 5 1HZ 100KHZ ac .noise voutbuffer gnd \*.measure tran delay trig v(clk) val=1 rise=2 targ v(voutbuffer) val=0 fall=2 dn(MNMOS 2,ID) .print noise 0.000001HZ 10000000000HZ dec 5 \*.ac \*.print voutbuffer clk \*.print ac vm(voutbuffer)

\*.print p(VVoltageSource\_1) .end

#### CONCLUSION

The DSBSC modulator circuit is designed with MOS transistor having channel length of 150nm. Power drawn from the message source is about 23 micro watt. Power consumption in CMOS inverter section is of the order of nano watt .Power consumed in each of  $10K\Omega$  resistance in inverting amplifier block is 1.25 ×10<sup>-5</sup> Watt. Delay measured from clock input to buffer amplifier output is 1.33ps.Higher cut off frequency from frequency response plot is around 188GHz. Thermal noise found at the buffer output terminal is due to channel resistance of one of the MOS transistor in the modulator section is of the order of 10-24 Volt<sup>2</sup> /Hz. Although the amount of noise is very less and tense to zero sometimes this amount of noise is also considered along with other types of noises for design purpose .The circuit of figure1 can be fabricated in two way : considering D and E block only and connecting B and F block externally or considering all B,C,D,E,F blocks. If one would like to fabricate the circuit considering later option it is necessary to replace the equivalent of voltage controlled voltage source in both B and F block by circuit using Mos transistor. It is also necessary to use lower resistance irrespective of using 10 K $\Omega$  resistances because fabrication of very high value resistance takes very large space and circuit becomes bulkier.

# REFERENCES

[1] Montree KUMNGERN," New Chopper Modulators Using Differential Volatge Current Conveyor," Radio Engineering, vol.20, no.2, june 2011.

[2] SMITH,K.,SEDRA,A,"The Current Conveyor-A New Circuit Building Block",IEEE Proceeding,1968,vol.56,p.1368-1369.

[3] Ginju V George, Jithisha Unnikrishnan, M R Baiju," Switched Capacitor Based Ring Modulator Using Differential volatge current conveyor", MIPRO 2011, May 23-27, 2011, Opatija, Croatia.

[4] Mouna Karmani , Chiraz Khedhiri , Belgacem Hamdi , ka Lok Man , Chi-Un Lei "A Fault A Fault- A Fault---tolerant 32 nm CMOS Double Sideband tolerant 32 nm CMOS Double Sideband AmplitudeSuppressed Carrier Modulator- Amplitude Suppressed Carrier Modulator--Demodulator Demodulator Circuit Implementation" IJCSI International Journal of Computer Science Issues, Vol. 9, Issue 3, No 2, May 2012 ISSN (Online): 1694-0814.

- [5] Behzad Razavi, Design of Analog CMOS Integrated Circuits, Tata McGraw-Hill, 2002.

- [6] Muhammad H.Rashid, Introduction to PSpice® Using OrCAD®

- for Circuits and Electronics, Prentice-Hall of India ,2005.

- [7] Allen ,Holberg , CMOS Analog Circuit Design ,Oxford University Press,2004.

Weste ,Harris , Banerjee , CMOS VLSI Design A Circuits and [8] Systems perspective, Pearson Education, 2005

[9] Kang and Leblebici , CMOS Digital Integrated Circuits Analysis and Design, Tata McGraw-Hill ,2003

[10] Baker, Harry, Boyce, CMOS Circuit Design , Layout , And Simulation, PHI,2003.

[11] Gray, Hurst, Lewis , Meyer , Analysis and Design of Analog Integrated Circuits, Wiley, 2010.

[12] Uyemura , VLSI Circuits and Systems , Wiley ,2002.

#### Tarun Samaddar

He has passed his M.Tech from Calcutta university in the year 2009 in Radio Physics and presently works as an Assistant Professor in Gargi Memorial Institute Of Technology, Baruipur in Electronics department .His research interest includes devices .

Debanjana Ray

She has passed her M.tech from National Institute Of Technical Teachers Training And Research (under MHRD) in Mechatronics in the year 2012 and presently works as an Assistant Professor in Gargi Memorial Institute Of Technology, Baruipur in Electronics department .Her research interest includes sensors &wireless communication .One of her papers has been accepted in an International jounal (IJERT) and 2 papers has been accepted in two national conferences.

# Authors profile

Bipasha chakrabarti

She has passed her M.tech from Narula Institute Of Technology in Electronics And Communication in the year 2013 and presently works as an Assistant Professor in Gargi Memorial Institute Of Technology, Baruipur in Electronics department .Her research interest includes communication .One of her papers has been accepted in an international journal (IJERT) and 3 papers has been accepted in three national conferences.

She has passed her M.tech degree from JIS of engineering, kalyani in Electronics college And Communication in the year 2012 and presently works as an Assistant Professor in Gargi Memorial Institute Of Technology, Baruipur in Electronics department .Her research interest includes wireless communication .One of her papers has been accepted in an international jounal (IJERT) and 1 paper has been accepted in a national conference.

# **IJSER**